# **Technical Data**

**WATKINS-JOHNSON**

March 1996

# Digital Demodulator WJ-9482-1

(International Version)

# **Description**

The WJ-9482-1 Digital Demodulator uses advanced digital signal processing (DSP) and surface mount technology to achieve high-performance precision demodulation of received signals in a compact, low-cost package. The unit accepts a 140-MHz IF input (160-MHz optional), performs demodulation of low-to high-rate PCM signals, and provides a decoded-symbol data output in a word parallel format. An input automatic gain control (AGC) circuit allows operation of the demodulator with an analog input level ranging from -30 to -10 dBm.

The WJ-9482-1's flexible DSP-based architecture allows the implementation of any IF bandwidth between 1 and 56 MHz. WJ's standard set of filters provides 96 bandwidths from 1 to 56 MHz.

The WJ-9482-1 supports BPSK, QPSK, SQPSK, 8 PSK, and 16 QAM demodulation modes. It also supports symbol rates up to 40 Mbaud, as well as a selection of absolute or differential encoding, and symbol-bit mapping. Sophisticated DSP-based adaptive algorithms provide acquisition and tracking of the symbol timing error, residual carrier offset, and equalizer tap updates. The WJ-9482-1 supports a 32-tap fractionally spaced T/2

### **Features**

- ☐ Low-cost precision demodulator

- □ BPSK, QPSK, SQPSK, 8 PSK, 16 QAM, demodulation modes

- □ 140-MHz IF input (160-MHz optional)

- ☐ Input signal rates from 1 to 40 Mbaud

- ☐ Selectable absolute or differential encoding

- □ Self-training 32-Tap T/2-spaced adaptive equalizer (16-Tap for SQPSK)

- ☐ Flexible symbol-bit mapping

- ☐ *Ethernet remote control*

- ☐ Built-in test capability to detect faults to circuit card level

- $\square$  1.75 in (3.86 cm) high full-rack package

HEIGHT

1.75 in (4.44 cm)

DEPTH\*

20 in (50.26 cm)

WIDTH

19 in (48.26 cm)

WEIGHT

20 lbs, max (9.05 kg

\* Excluding connectors & handles

#### **WATKINS-JOHNSON COMPANY**

700 Quince Orchard Road, Gaithersburg, Maryland 20878-1794 Phone: (800) WJHELPS or +(301) 948-7550

FAX: +(301) 921-9479 Email: wj.helps@wj.com Website: www.wj.com

All International sales of WJ equipment are subject to USA export license approval.

This material provides up-to-date general information on product performance and use. It is not contractual in nature, nor does it provide warranty of any kind.

equalizer for all demodulation modes, except SQPSK. For SQPSK, the unit supports a 16-tap T/2-spaced equalizer.

The WJ-9482-1's 32-bit microprocessor circuitry permits powerful local or remote control. An operator can transfer all control and status information through a TCP/IP-compliant ethernet interface. The unit's built-in test software allows location of faults to the circuit card level.

For all of its capability, the WJ-9482-1 is extremely compact and is contained in a single 1.75 by 19 by 20 inch (4.44 by 48.26 by 50.80 cm) rack-mount enclosure. The unit weighs approximately 20 pounds.

# **Functional Description**

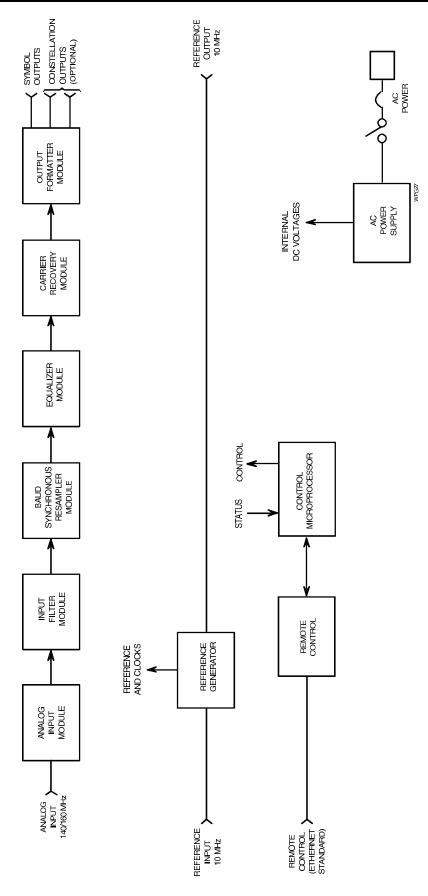

The functional block diagram in Figure 1 shows the standard and optional modules that make up the WJ-9482-1 Digital Demodulator. The unit accepts a 140-MHz IF input (160-MHz optional). A 56-MHz SAW filter band limits the input prior to conversion to baseband and digitization. An AGC circuit maintains an acceptable signal level into the analog-to-digital (A/D) converter that digitizes the analog input signal at a 162-MSPS rate with 8 bits of precision. The resulting digital baseband is then available for subsequent processing.

The digital demodulator subsystem incorporates three advanced very large-scale integration (VLSI) application-specific integrated circuits (ASIC), which are designed and optimized for wideband pulse code modulation (PCM) demodulation. These ASICs include:

- Digital filter chip for input filtering and adaptive equalization

- Digital resampler to digitally resample the input data at a rate synchronous with the baud rate

- Digital mixer chip to remove carrier offsets

Incorporating these ASICs provides a significant size, cost, and complexity savings.

After digitization, the WJ-9482-1 digitally performs all the remaining processing functions. The demodulator filters and decimates the digital baseband commensurate with the desired band rate. This

extracts the desired signal, and eliminates out-of-band signals and excess noise. Applying additional AGC optimizes the inband signal power. The unit then synchronously resamples the predetected data stream at exactly twice the baud rate. A 32-tap T/2-spaced complex adaptive equalizer accepts the baudsynchronous data and generates the equalized symbol data at the baud rate. (NOTE: For the SOPSK demodulation mode, the equalizer is a 16-tap T/2spaced complex adaptive equalizer that continues to output data at twice the baud rate.) Finally, a carrierremoval ASIC removes any residual carrier offset in the resultant symbol data and performs symbol alignment for SQPSK. The Output Formatter Module carries out the final symbol estimation, performs the appropriate symbol decoding, and outputs the demodulated symbols.

The WJ-9482-1 provides symbol-timing loop, carrier-recovery loop, and equalizer-tap update algorithms on three general-purpose DSP processors. This approach allows optimization of the algorithm implementations for specific modulation formats. It also allows significant flexibility in controlling loop dynamics during the acquisition and tracking phases. The processors provide analysis data including:

- Actual baud rate

- Actual residual carrier offset

- Signal quality estimate

- Snap-shot data representing the demodulated constellation

A 32-bit control processor provides overall control of the unit. In particular, the microprocessor carries out initialization, built-in test, and input/output of control and status through the ethernet interface.

# **System Applications & Options**

Several WJ-9482-1 features facilitate the integration of the unit within a system. The modular construction allows easy maintenance with a minimum of downtime. A thorough built-in test capability permits the quick detection and isolation of hardware faults to the circuit card level. The basic WJ-9482-1 configuration accepts a 140-MHz IF input and provides decided-symbol data output. Options include a 160-MHz IF input capability (WJ-9482/160).

Figure 1. WJ-9482-1 Functional Block Diagram

# **Specifications**

| Analog Input Characteristics IF Input | 140 MHz (160-MHz ontional)               |

|---------------------------------------|------------------------------------------|

| Bandwidth                             |                                          |

|                                       |                                          |

| Input Levels                          |                                          |

| Noise Figure                          |                                          |

| Input VSWR                            |                                          |

| Input Overload                        |                                          |

| Input Impedance                       | . 50 ohms                                |

| Image Rejection                       | . 60 dB                                  |

| Gain Control                          | . Manual or automatic                    |

| Manual Gain Control Range             | . 30 dB                                  |

|                                       |                                          |

| Demodulator Characteristics           |                                          |

| Detection Modes                       |                                          |

| Baud Rates                            | . 1 to 40 Mbaud                          |

| Equalization                          | . CMA for acquisition, DD for tracking   |

| Equalizer Taps                        |                                          |

| Tap Spacing                           |                                          |

|                                       | 1 =/= 5ymbol penou                       |

| Digital Output Characteristics        |                                          |

| Symbol Format                         | . N data bits with baud clock, where N = |

|                                       | number of bits per symbol                |

| ll                                    | . ,                                      |

| Output Levels                         |                                          |

| Output Clock                          |                                          |

|                                       | 50% <u>+</u> 5%)                         |

| Output Connector                      | . 50-pin D                               |

|                                       | •                                        |

| Control                               |                                          |

| Remote                                | . Ethernet AUI                           |

| Frequency Reference                   |                                          |

|                                       | 1 v 10-6 may                             |

| Internal Reference Stability          |                                          |

| Extrnal Reference Input               | . 10 MHz, 200 mv into nign impedance     |

| Physical/Environmental                |                                          |

| Operating Temperature Range           | 0 to 50°C                                |

| Altitude                              |                                          |

|                                       |                                          |

| Power Requirement                     |                                          |

| Power Consumption                     | . 115 vv, max                            |

|                                       |                                          |